的了解还停留在Protel99se的时代。几天前 ,一个客户发来一个AD的原理图,希望能做出

最初尝试将AD的原理图转为OrCAD的原理图进行设计,而且现在OrCAD17.4的软件也可以很方便的将AD的PCBDOC文件转成ORCAD的DSN文件。

但转换后发现一个问题,AD的原理图中不同页码中相同的网络,转成了DSN文件中,这些网络名字后面都被加了“_1、”_2等变成了不同的网络,这样实际相同的网络都没法连接起来。

经过研究才发现,这个是软件间不同的使用Ruler造成的,在OrCAD中不同页码之间相同的网络,一定要通过跨页连接符offpage来定义连接,在AD中则不需要,只要定义相同的Net label,就直接默认连接起来。这就造成了AD的原理图转换到OrCAD后,Net label虽然在的,但页码之间没有offpage,OrCAD就认为不是相同的网络。

重新添加offpage工作量很大,而且AD中原理图和PCB封装名字和属性都习惯用小数线、空格之类的,这些在OrCAD中都不支持的,导致即使原理图可以用,导Netlist时也会report出来很多问题,只有把这些名字中非法字符更改后,才能顺利导出Netlist文件。关键是EDA工程师对原理图不熟悉,更改原理图后可能会产生一些不可控的问题出现会影响到PCB设计端。

几番衡量之后,还是决定将客户的原理图导出网表后,将Netlist的网表导入到Cadence Allegro中进行PCB设计,感谢行业资深工程师陈工提供的Netlist转换工具,先将具体的方法分享给大家。

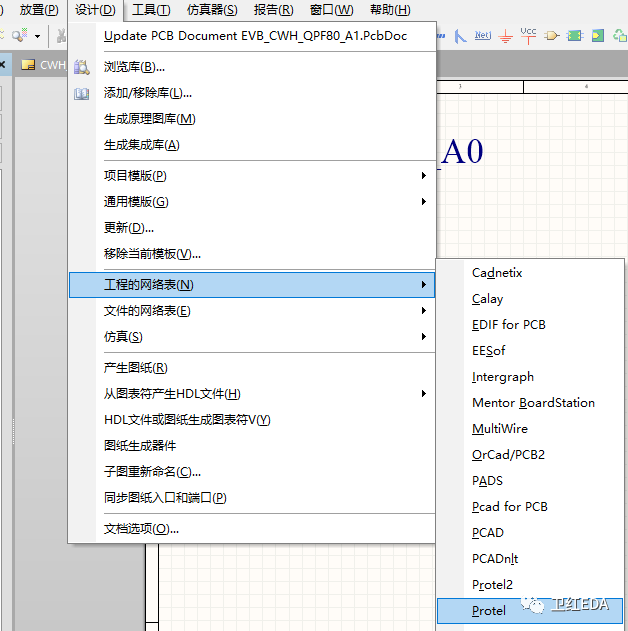

1、先将AD的原理图,导出Protel格式的Netlist文件,操作如下图所示,要导出整个工程的网表,不是某页的网表;

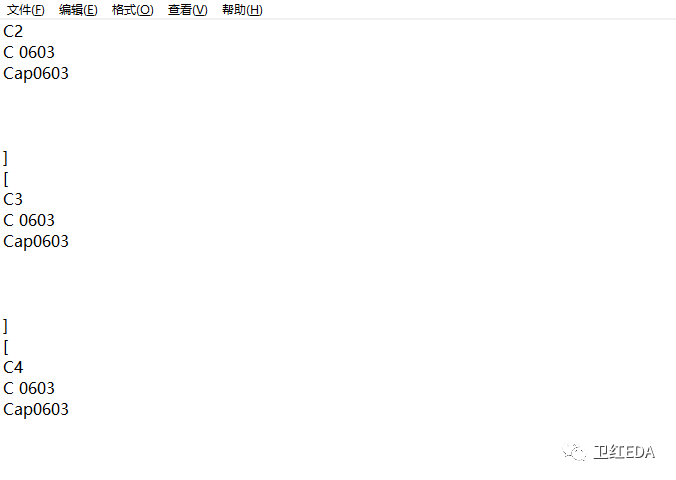

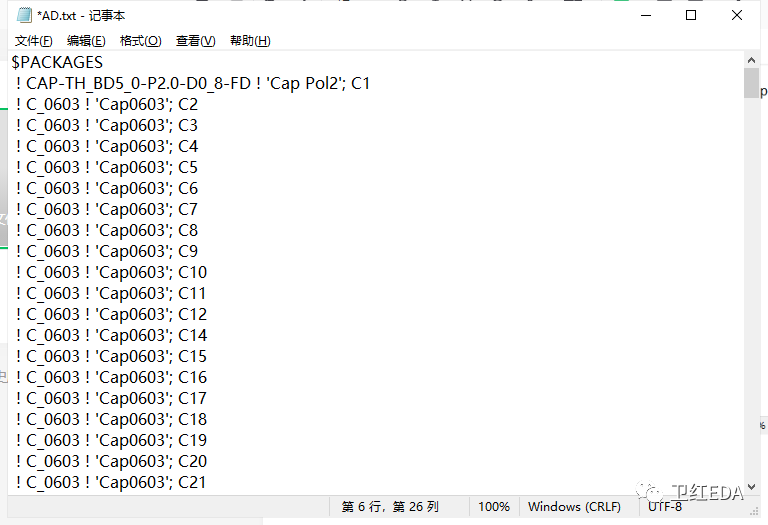

2、Protel格式的Netlist文件后缀名是net的,用记事本打开后,是这个样子,如下图所示,这个格式显然是Allegro不能识别的,我们应该将Netlist文件进行转换下;

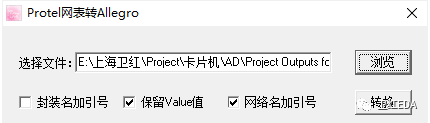

3、打开Protel网表转Allegro.exe的程序文件,选择Protel格式的Netlist文件,其他默认选择,点击转换进行网表格式转换;

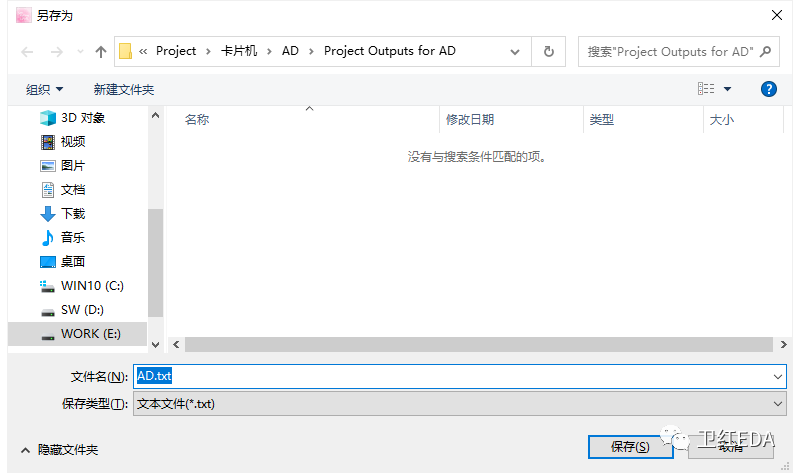

4、用记事本打开转换成的txt文件,能够正常的看到文件格式转换已经好了,但名字中出现了很多小数点和空格的非法字符,这个挺麻烦,就需要手动去修改下,如果这款软件能自动把小数点和空格自动改为Underline,那就更方便了;

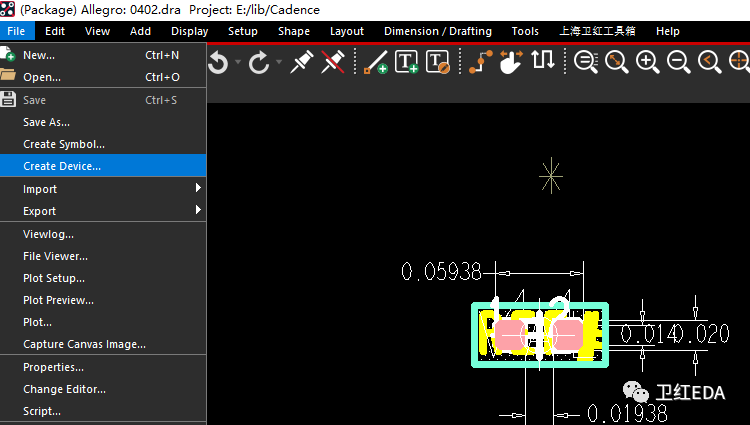

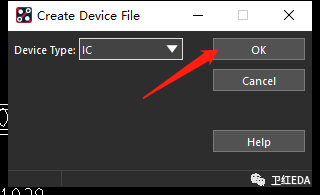

6、还有一点的就是PCB封装不仅要有dra文件、symbol文件,还要有device文件,这个能打开dra文件,然后执行Creat Device,如下图所示;

直接点击OK就生成了一个txt的device文件,操作虽然很简单,但架不住封装数量多,可以做个批处理的脚本文件来自动执行;

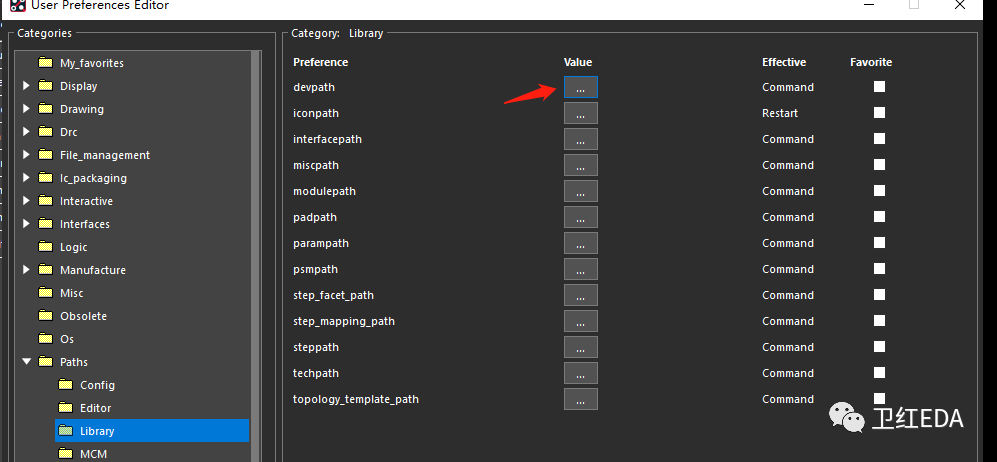

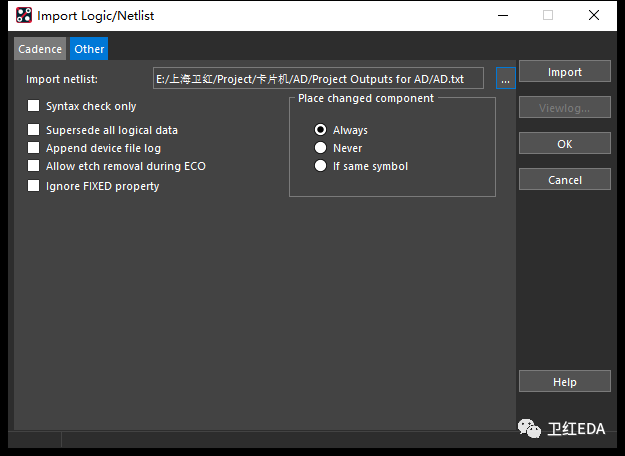

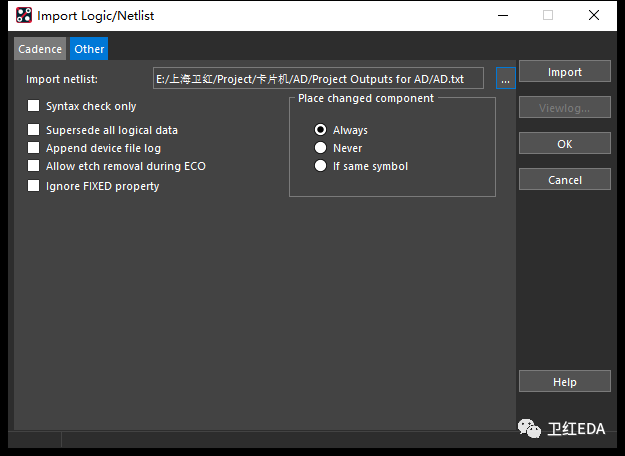

7、最后就需要将更改后的Netlist文件导入到Allegro的PCB文件中了,导入后可能会出现很多的报错信息出现,比如device文件找不到, 需要有很大的耐心去处理。

布局一致性差,导致硬件测试时每个部分都要重复测试,耗时又繁琐。下面就介 绍

,多通道电路设计,大幅度的提升工作效率,以上问题都能够获得很好 的解决。这里有点类似我们写程序的时候, 把

ESP 连接到 Openhab 并控制灯、RGB-LED 等。 所以我的问题:是

上注明了详细的原理说明以及需要注意的几点;考虑周全的设计,例如电源防反接设计、电源输入兼备插针插座、大面

windows-redis-memcahed redis和memcache集成快速使用包

【Longan Pi 3H 开发板试用连载体验】给ChatGPT装上眼睛,并且还可以语音对线,FastAPI服务器搭建与TTS播放

【Longan Pi 3H 开发板试用连载体验】给ChatGPT装上眼睛,并且还可以语音对线,音频采集

【米尔-瑞米派兼容树莓派扩展模块-试用体验】基于ROS系统的三麦轮小车自主导航